top of page

Unit 3.1.1 Sequental Logic

Unit 3.2 AsynchronousCounters

This is a picture of the timing of a J/K Flip-Flop.

This is a picture of a 3-Bit Binary Down Counter implemented with 74LS76 J/K flip-flops. This design will count from 7 to 0 and then repeat.

This is a picure of a counter that counts to 30 minutes. Once the timer reaches 30 minutes it will reset to 0 and start again.

This circuit with the 4 displays will count to 1000 starting from the bottom (ones place) to the top (thousandths place).

Unit 3.3 Synchronous Counters

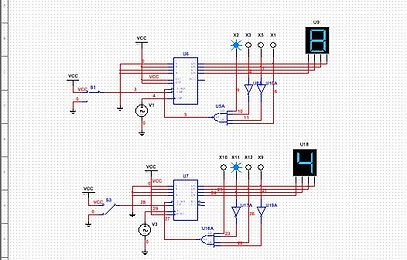

This is unit 3.3.1 Synchronous counter. When the switch is flipped, the counter will count from 0 to 7 and then restet back to 0.

This is unit 3.3.2 Synchronous counter. When both switches are flipped, the counters will count from 2 to 9 adn reset.

This is unit 3.3.1 Synchronous counter. When the switch is flipped, it will count down from HEX D to 6.

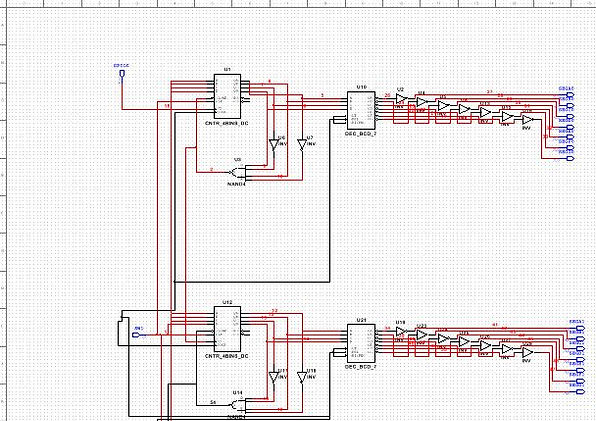

This is a 0 to 99 Synchronous counter on a PLD design.

This is a 999 Synchronous counter on a PLD design.

This is a Synchronous secret message that displays Ping-Pong is life -_-.

bottom of page